軟件架構圖是軟件開發過程中的重要工具,它展示了系統各組件的組織結構與交互方式。在基礎軟件服務層面,架構圖尤其關鍵,因為它定義了支撐上層應用的核心服務結構。本文將詳細介紹基礎軟件服務在軟件架構圖中的組成與作用。

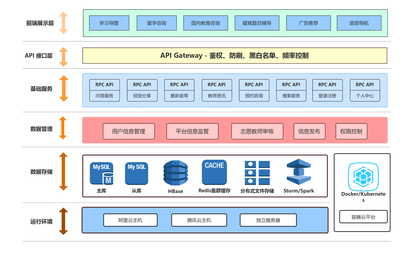

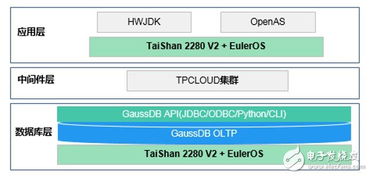

基礎軟件服務通常包括操作系統、數據庫管理系統、中間件、網絡服務等核心組件。在架構圖中,這些服務位于底層,為應用層提供穩定、高效的運行環境。操作系統負責硬件資源的管理與調度;數據庫管理系統處理數據的存儲、查詢與事務;中間件充當分布式系統中的通信橋梁;網絡服務則確保系統間的數據傳輸安全可靠。

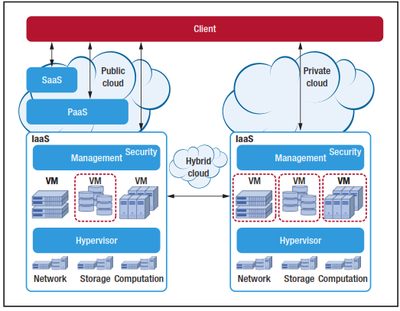

設計基礎軟件服務架構時,需考慮高可用性、可擴展性與安全性。例如,通過負載均衡與集群技術提升服務可用性;采用微服務架構實現模塊化擴展;結合加密與訪問控制機制保障數據安全。清晰的架構圖不僅能幫助團隊理解系統依賴,還能輔助性能優化與故障排查。

基礎軟件服務是軟件系統的基石,其架構圖的設計直接影響系統的穩定與演進。開發者應結合實際需求,繪制詳實且易讀的架構圖,以確保軟件項目的成功實施。