在數(shù)字經(jīng)濟與國家安全戰(zhàn)略的雙重驅(qū)動下,信息技術(shù)應(yīng)用創(chuàng)新產(chǎn)業(yè)已成為中國科技自立自強的關(guān)鍵陣地。一個顯著的趨勢是,中國信創(chuàng)產(chǎn)業(yè)的發(fā)展動力,正從單一的技術(shù)突破或產(chǎn)品替代,轉(zhuǎn)向更為復(fù)雜、更具生命力的生態(tài)融合。這種以應(yīng)用軟件和服務(wù)為重要抓手的融合進程,正在重塑產(chǎn)業(yè)格局,并展現(xiàn)出勢不可擋的發(fā)展勢頭。

一、從“單品突破”到“系統(tǒng)協(xié)同”:生態(tài)融合成為新范式

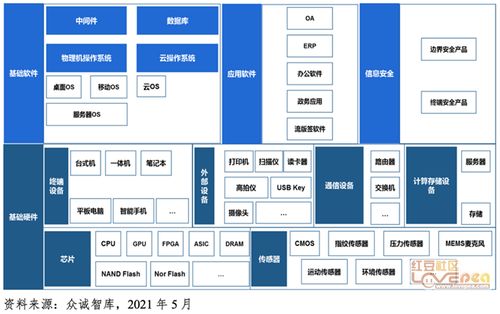

早期信創(chuàng)發(fā)展多聚焦于CPU、操作系統(tǒng)、數(shù)據(jù)庫等基礎(chǔ)軟硬件的“可用”與“好用”。信息技術(shù)體系的價值最終體現(xiàn)在支撐上層業(yè)務(wù)應(yīng)用。當(dāng)前,領(lǐng)先的中國廠商正深刻意識到,沒有繁榮的應(yīng)用生態(tài),基礎(chǔ)軟硬件就如同無源之水。因此,產(chǎn)業(yè)發(fā)展的重心自然延伸至應(yīng)用軟件與服務(wù)層面。

這種融合體現(xiàn)在多個維度:

- 縱向融合(技術(shù)棧整合):基礎(chǔ)硬件廠商、操作系統(tǒng)廠商、中間件與數(shù)據(jù)庫廠商、應(yīng)用軟件開發(fā)商及系統(tǒng)集成商,正打破傳統(tǒng)壁壘,組建深度適配的聯(lián)合體。例如,國產(chǎn)CPU與操作系統(tǒng)廠商主動開放接口、提供優(yōu)化工具,攜手辦公軟件、行業(yè)應(yīng)用軟件(如金融、能源、政務(wù)核心系統(tǒng))進行深度適配與性能調(diào)優(yōu),確保從底層到應(yīng)用層的全棧順暢運行。

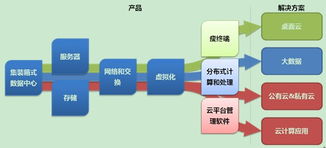

- 橫向融合(產(chǎn)業(yè)協(xié)同):不同領(lǐng)域的信創(chuàng)企業(yè),如云計算巨頭、網(wǎng)絡(luò)安全公司、行業(yè)軟件龍頭,通過戰(zhàn)略合作、共建實驗室、成立產(chǎn)業(yè)聯(lián)盟等方式,共同定義標(biāo)準(zhǔn)、開發(fā)解決方案。例如,針對金融、電信等關(guān)鍵行業(yè),形成從底層基礎(chǔ)設(shè)施到上層業(yè)務(wù)應(yīng)用的全棧式、一體化信創(chuàng)解決方案。

- 跨界融合(場景驅(qū)動):信創(chuàng)生態(tài)與云計算、人工智能、大數(shù)據(jù)、物聯(lián)網(wǎng)等新興技術(shù)生態(tài)加速融合。國產(chǎn)應(yīng)用軟件積極擁抱云原生、微服務(wù)架構(gòu),信創(chuàng)云平臺則集成各類SaaS化應(yīng)用服務(wù),共同服務(wù)于數(shù)字化轉(zhuǎn)型的復(fù)雜場景。

二、應(yīng)用軟件與服務(wù):生態(tài)融合的“黏合劑”與“價值放大器”

應(yīng)用軟件與服務(wù)在生態(tài)融合中扮演著不可或缺的核心角色:

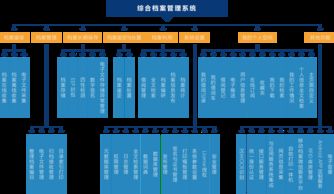

- 需求牽引:行業(yè)用戶的真實業(yè)務(wù)需求,通過具體的管理軟件、業(yè)務(wù)系統(tǒng)、辦公協(xié)同工具等應(yīng)用直接體現(xiàn)。這些需求倒逼底層技術(shù)不斷優(yōu)化,是驅(qū)動全棧技術(shù)協(xié)同創(chuàng)新的原動力。

- 體驗定義:終端用戶對信創(chuàng)體系的接受度,最終取決于其上運行的應(yīng)用程序是否流暢、功能是否完備、交互是否友好。優(yōu)秀的應(yīng)用軟件是提升信創(chuàng)產(chǎn)品用戶體驗、贏得市場口碑的關(guān)鍵。

- 價值實現(xiàn):信創(chuàng)的最終目標(biāo)是支撐國民經(jīng)濟各行業(yè)的數(shù)字化轉(zhuǎn)型與安全運營。只有豐富的行業(yè)應(yīng)用軟件(如工業(yè)設(shè)計軟件、ERP、CAD、EDA等)和服務(wù)(如運維、咨詢、培訓(xùn))成熟落地,信創(chuàng)產(chǎn)業(yè)的經(jīng)濟價值和社會價值才能充分釋放。

三、廠商主導(dǎo)的生態(tài)建設(shè):構(gòu)筑護城河與加速普及

以華為、中國電子、中國電科、浪潮、阿里云、騰訊等為代表的頭部廠商,已成為生態(tài)融合的主要推動者。它們通過“硬件開放、軟件開源、使能伙伴”等策略,構(gòu)建起以自身技術(shù)體系為核心的“根生態(tài)”。

- 開源共建:通過開放源代碼(如OpenHarmony、OpenEuler)、貢獻核心代碼等方式,降低應(yīng)用開發(fā)門檻,吸引廣大軟件開發(fā)者和企業(yè)加入生態(tài)。

- 開發(fā)者賦能:提供豐富的開發(fā)工具套件(SDK/DevKit)、模擬環(huán)境、培訓(xùn)認證和開發(fā)基金,全力培育應(yīng)用生態(tài)。

- 聯(lián)合解決方案:與垂直行業(yè)的軟件ISV(獨立軟件開發(fā)商)深度合作,共同打造經(jīng)過認證的聯(lián)合解決方案,快速覆蓋重點行業(yè)市場。

這種由平臺型廠商主導(dǎo)、多方參與的生態(tài)模式,極大地加速了應(yīng)用軟件的適配與創(chuàng)新,形成了“基礎(chǔ)平臺不斷優(yōu)化 → 應(yīng)用生態(tài)日益豐富 → 用戶群體持續(xù)擴大 → 反哺基礎(chǔ)平臺投入”的正向循環(huán)。

四、挑戰(zhàn)與未來展望

盡管勢頭強勁,生態(tài)融合仍面臨挑戰(zhàn):不同技術(shù)路線之間的兼容性、跨平臺應(yīng)用的開發(fā)與遷移成本、關(guān)鍵行業(yè)核心應(yīng)用軟件的成熟度、復(fù)合型人才的短缺等。

中國信創(chuàng)產(chǎn)業(yè)的進一步發(fā)展將更加依賴于生態(tài)融合的深度與廣度:

- 向核心業(yè)務(wù)系統(tǒng)縱深:從辦公、管理類應(yīng)用向生產(chǎn)核心、研發(fā)設(shè)計類等高價值、高復(fù)雜度應(yīng)用突破。

- 擁抱云化與智能化:信創(chuàng)應(yīng)用將全面向云原生演進,并與AI大模型深度融合,催生智能化的新一代應(yīng)用軟件與服務(wù)。

- 構(gòu)建開放標(biāo)準(zhǔn)體系:在競爭合作中,逐步形成廣泛認可的接口規(guī)范與標(biāo)準(zhǔn),促進不同生態(tài)間的互聯(lián)互通,走向更開放的“大生態(tài)”。

- 深化國際合作:在確保安全可控的前提下,吸引全球開發(fā)者與優(yōu)質(zhì)應(yīng)用加入中國主導(dǎo)的信創(chuàng)生態(tài),提升國際影響力。

###

中國信創(chuàng)產(chǎn)業(yè)已駛?cè)胍浴吧鷳B(tài)融合”為標(biāo)志的新發(fā)展階段。以應(yīng)用軟件與服務(wù)為關(guān)鍵樞紐,全產(chǎn)業(yè)鏈廠商正從“單點突圍”走向“集團軍作戰(zhàn)”。這股由內(nèi)而外、自上而下匯聚的融合之力,不僅夯實了國家信息技術(shù)體系的根基,更將賦能千行百業(yè)的數(shù)字化其發(fā)展之勢, indeed, 勢不可擋。